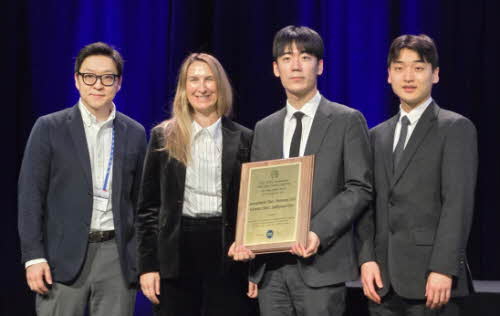

서울대학교 공과대학은 전기정보공학부 최재혁 교수 연구팀(서정범·조윤서·신유환·최재혁)이 지난 16일 미국 샌프란시스코에서 열린 세계 최고 권위의 ‘국제고체회로학회(ISSCC) 2026’에서 최우수 논문상인 ‘ISSCC 2025 Takuo Sugano Award’를 수상했다고 밝혔다.

전기전자공학자협회(IEEE)가 주관하는 ISSCC는 1954년 설립된 이후 올해로 73회를 맞았으며, 반도체 집적회로 설계 분야에서 최대 규모를 갖춘 국제 학술대회다. 매년 글로벌 기업과 대학의 최첨단 반도체 기술이 최초 공개되는 자리로, 업계에서는 ‘반도체 설계 올림픽’으로 불릴 만큼 그 상징성이 크다.

Takuo Sugano Award는 매년 ISSCC에서 발표되는 아시아·태평양 지역의 논문들 가운데, 높은 기술적 완성도는 물론이고 학문적·산업적 파급력을 동시에 인정 받은 단 한 편에 수여하는 최고 권위의 논문상이다. ISSCC 2025에서는 아·태 지역에서 총 165편의 논문이 발표된 바 있다.

최 교수팀의 이번 수상은 지난 ISSCC 2005에서 서울대 연구팀이 수상한 이후 20년 만에 거둔 쾌거로 주목받고 있다. 특히 한국의 반도체 회로 설계 연구가 갖춘 세계적인 경쟁력을 국제 학계에서 또 한번 입증한 성과로 평가된다.

‘An 850μW 2-to-5GHz Jitter-Filtering and Instant-Toggling Injection-Locked Quadrature-Clock Generator for Low-Power Clock Distribution in HBM Interfaces’ 제하의 수상 논문은 AI 시스템의 핵심 반도체인 고대역폭 메모리(HBM)의 가장 큰 난제로 꼽히는 전력 소모 및 발열 문제를 획기적으로 해결할 수 있는 새로운 회로 설계 기법을 제시했다.

최신 HBM은 GPU와 메모리 간의 초고속 데이터 처리를 위해 2000개 이상의 데이터 입출력을 동시에 구동해야 한다. 그런데 이 과정에서 수 기가헤르츠(GHz) 대역의 다중위상 고주파 신호를 분배하기 위해 막대한 전력이 소모된다. 이는 HBM 발열의 가장 큰 원인으로 지적돼 왔다.

이 문제의 해결에 나선 최 교수팀은 고주파 다중위상 신호를 병렬 분배하는 기존 방식 대신, 하나의 저주파 신호에 위상 정보를 직렬·순차적으로 담아 전송한 뒤 데이터 입출력 직전에 복원하는 새 구조를 제안했다. 그리고 이를 통해 기존 방식 대비 전력 소모를 10분의 1 수준 미만으로 줄이는 데 성공했다.

논문의 제1저자인 서정범 박사과정 연구원은 “대한민국 반도체 산업의 핵심인 HBM 분야의 발전에 실질적으로 기여할 수 있는 기술을 개발하게 돼 매우 기쁘다”며 “앞으로 치열한 글로벌 경쟁 속에서도 국내 반도체 산업의 입지를 더욱 공고히 할 수 있도록 책임감을 갖고 연구에 매진하겠다”고 수상 소감을 밝혔다.